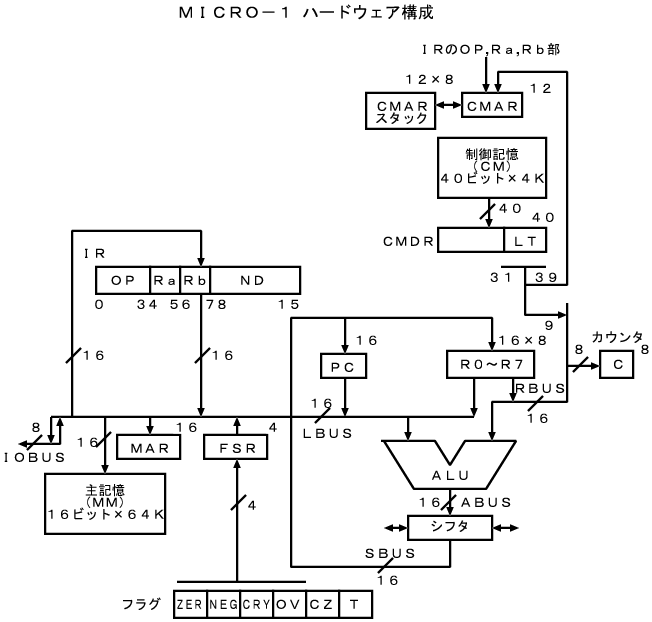

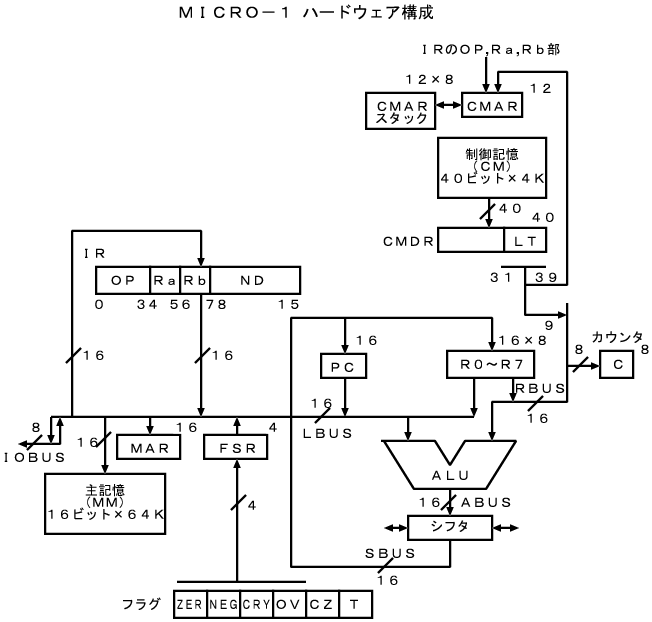

| 機能ユニット名 | 略語 | ビット長 | 機能 |

| 制御記憶 | CM | 40ビット×4K | マイクロプログラムを格納する。 |

| 制御記憶 アドレスレジスタ |

CMAR | 12ビット | 制御記憶のアドレスを指定する。 |

| CMARスタック | - | 12ビット×8 | マイクロサブルーチンのための戻りアドレスを保持する。 |

| 制御記憶 データレジスタ |

CMDR | 40ビット | 読み出したマイクロ命令を保持する。 |

| マイクロ命令の LTフィールド |

LT | 9ビット | CMARへのアドレス生成とRBUSへのデータ生成に使用する。 |

| プログラム カウンタ |

PC | 16ビット | 機械命令のアドレスを保持する。 |

| 汎用レジスタ | R0〜R7 | 16ビット×8 | 演算の対象となるデータを置く。 |

| カウンタ | C | 8ビット | ループカウンタなどに使用する。 |

| 命令レジスタ | IR | 16ビット | 命令コード部(OP)、レジスタ指定部(Ra,Rb)、定数部(ND)からなる。 |

| フラグ | - | 各1ビット | ZER(ゼロ)、NEG(ネガティブ)、CRY(キャリー)、OV(オーバフロー)、 CZ(カウンタゼロ)、T(汎用)がある。 |

| フラグセーブ・ レジスタ |

FSR | 4ビット | フラグのうち先頭の4ビットを保持する。 |

| 算術論理演算装置 | ALU | - | 加減算、論理演算を行なう。 |

| シフタ | - | - | 1ビットの算術/論理/巡回シフトを行なう。 |

| 主記憶 アドレスレジスタ |

MAR | 16ビット | MMのアドレスを指定する。 |

| 主記憶 | MM | 16ビット×64K | 機械命令やデータを格納する。 |

| ALU左入力バス | LBUS | 16ビット | - |

| ALU右入力バス | RBUS | 16ビット | - |

| ALU出力/ シフタ入力バス |

ABUS | 16ビット | - |

| シフタ出力バス | SBUS | 16ビット | - |

| 入出力バス | IOBUS | 8ビット | 入出力機器との間でデータをやり取りするためのバス |

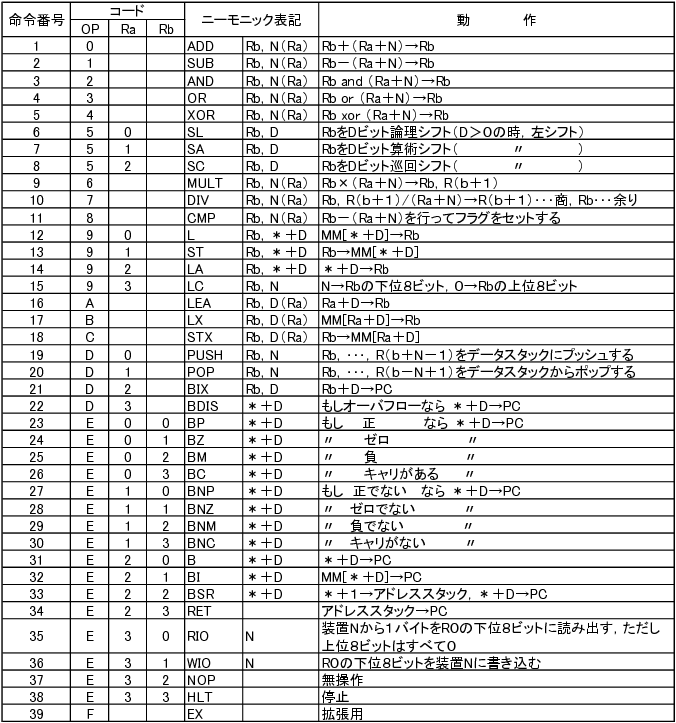

機械命令一覧

注意