埲壓偺奺壽戣僾儘僌儔儉傪嶌惉偟丄儗億乕僩偣傛丅

仸幙栤丒媈栤偼悘帪庴偗晅偗傞丅

儗億乕僩採弌婜尷丂2014擭8寧11擔(寧)

儗億乕僩偼

妛壢庼嬈巟墖僔僗僥儉 CoursePower偱採弌偡傞偙偲丅

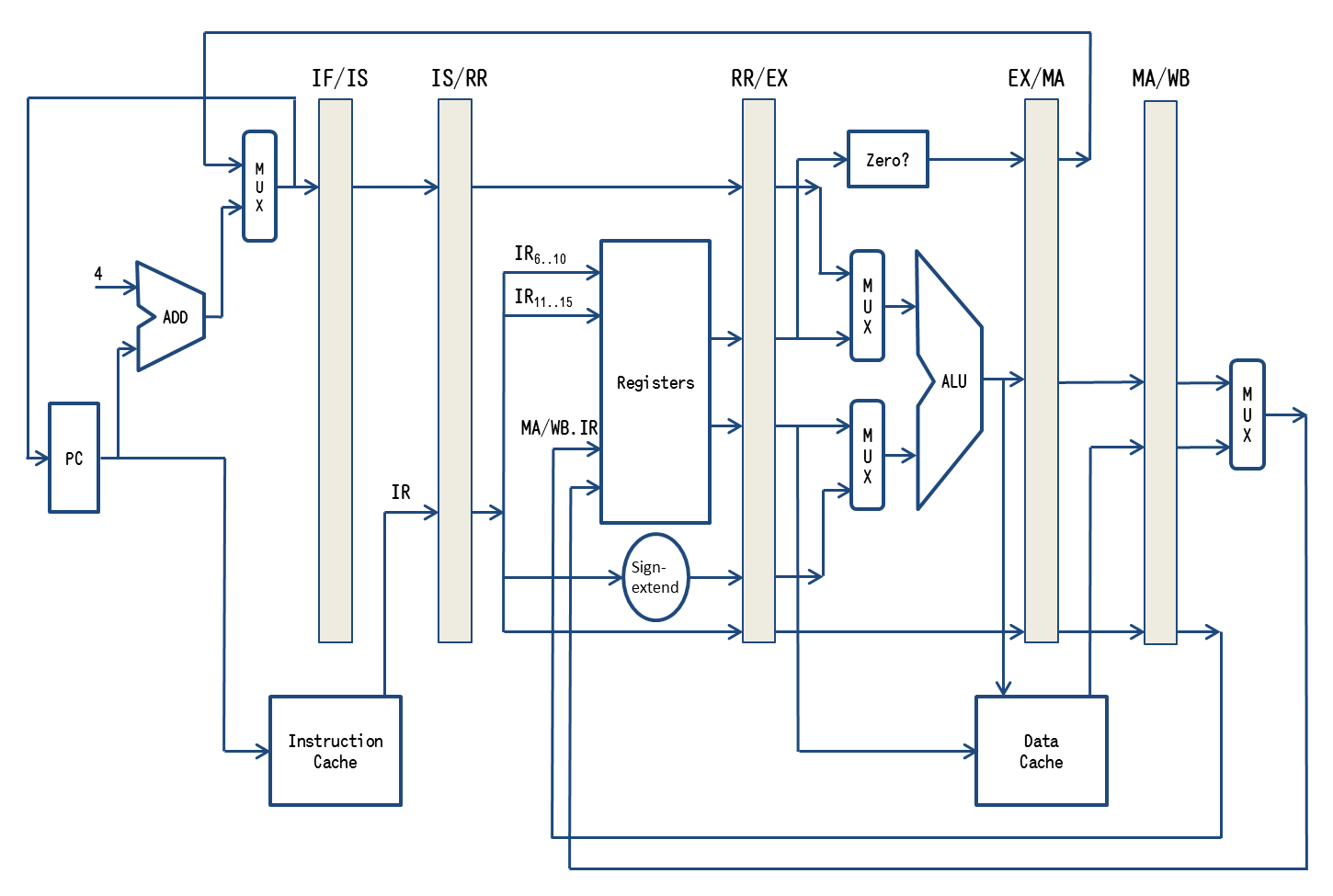

mipsy傪儀乕僗偲偟偰丄 6抜僷僀僾儔僀儞峔惉偲偡傞偙偲丅

婎杮揑側僷僀僾儔僀儞峔惉恾偼埲壓偺恾偵帵偡丅

(旕僷僀僾儔僀儞僔儈儏儗乕僞偱偼丄偙偺僷僀僾儔僀儞偺奺僗僥乕僕傪

柦椷僒僀僋儖偺1僒僀僋儖偛偲偵拃師揑偵張棟偟偰偄傞)

奺僗僥乕僕偱偺庡側張棟撪梕偼埲壓偺捠傝偱偁傞丅

A Simple Implementation of MIPS Pipeline (w/ 6-stage)

[IF stage (Instruction fetch First)]

request_read_to_cache(PC);

NPC = PC + 4;

[IS stage (Instruction fetch Second)]

IR = reply_read_from_cache(PC);

[RR stage (Register file Read)]

A = Regs[rs(IR)];

B = Regs[rt(IR)];

Imm = imm(IR); // sign-extended immediate field of IR

UImm = uimm(IR); // immediate field of IR

[EX stage (EXecution)]

Memory references:

ALUOutput = A + Imm;

request_read_to_cache(ALUOutput);

or

request_write_to_cache(ALUOutput, B);

Register-Register ALU Instruction:

ALUOutput = A func B;

Register-Immediate ALU Instruction:

ALUOutput = A func Imm;

Branch:

ALUOutput = NPC + (Imm << 2);

Cond = (A == 0);

[MA stage (Memroy Access)]

Memory references (Load instruction):

LMD = reply_read_from_cache(ALUOutput);

Branch:

if (Cond) PC = ALUOutput;

[WB stage (Write Back)]

Memory references (Load instruction):

Regs[rt] = LMD;

Register-Register ALU Instruction:

Regs[rd] = ALUOutput;

Register-Immediate ALU Instruction:

Regs[rt] = ALUOutput;

偙傟傪儀乕僗偲偟偰丄僨乕僞僴僓乕僪傪娚榓偡傞偨傔偺僨乕僞僼僅乕儚乕僨傿儞僌

婡擻傗丄惂屼僴僓乕僪傪娚榓偡傞偨傔偺暘婒愭嶼弌梡偺壛嶼婍丒暘婒忦審敾掕婍側偳傪

捛壛偡傞偙偲丅

巻柺偵偰攝晍偟偨帒椏

(Appendix-A Pipelining: Basic and Intermediate Concepts偺堦晹敳悎)傪

嶲峫偵偡傞偲傛偄丅

(偨偩偟丄攝晍帒椏偱偼 5抜僷僀僾儔僀儞峔惉傪慜採偲偟偰偄傞偺偱丄摉慠嵶晹偼堎側傞)

柦椷僷僀僾儔僀儞偺摦嶌傪昞帵偡傞婡擻傪晅偗丄

幚嵺偵僾儘僌儔儉傪摦嶌偝偣偨偲偒偺條巕傪昞帵偝偣傛丅

(偄傠偄傠昞帵傪岺晇偟偰僷僀僾儔僀儞偺摦嶌偑尒傗偡偔偡傞偲傛偄)

偨偩偟丄MIPS偺昗弨揑側(惍悢)忔嶼柦椷偼偙偺僷僀僾儔僀儞壔偵岦偐側偄偨傔丄

埲壓偺 3僆儁儔儞僪偺忔嶼柦椷傪捛壛偟丄偙偺柦椷傪幚峴偡傞偲偒偺傒僷僀僾儔僀儞

張棟偡傞傕偺偲偡傞丅

| opcode (6) | rs (5) | rt (5) | rd (5) | shmnt (5) | funct (6) |

| 0x1c | 0乣31 | 0乣31 | 0乣31 | 0 | 0x02 |

偙偺柦椷偼丄rs偱巜掕偟偨儗僕僗僞偺抣偲 rt偱巜掕偟偨儗僕僗僞偺抣傪忔偠丄寢壥偺愊偺

壓埵32價僢僩傪 rd偱巜掕偟偨儗僕僗僞偵奿擺偡傞丅

(愊偺忋埵32價僢僩偼幪偰傜傟傞)

偙偺柦椷傪巊偆偲偒偼埲壓偺傛偆偵婰弎偟偨忋偱

傾僙儞僽儖偡傞嵺偵丄"-mips32r2"僆僾僔儑儞傪晅偗傞丅 (晅偗朰傟傞偲丄 mult柦椷亄mflo柦椷偺2柦椷偵曄姺偝傟傞偺偱拲堄)/* file.S */ li $4,2 li $5,3 mul $2,$4,$5 /* 儗僕僗僞4斣偲5斣偺抣傪忔偠偰2斣偵奿擺 */

mipsel-elf-gcc -mips32r2 -O file.S -c mipsel-elf-ld file.o -Tmipsy.ld -o file.bin