以下の各課題プログラムを作成し、レポートせよ。(ただし、課題3はオプション課題)

※質問・疑問は随時受け付ける。

レポート提出期限 2013年8月12日(月)

レポートは

学科授業支援システム CoursePowerで提出すること。

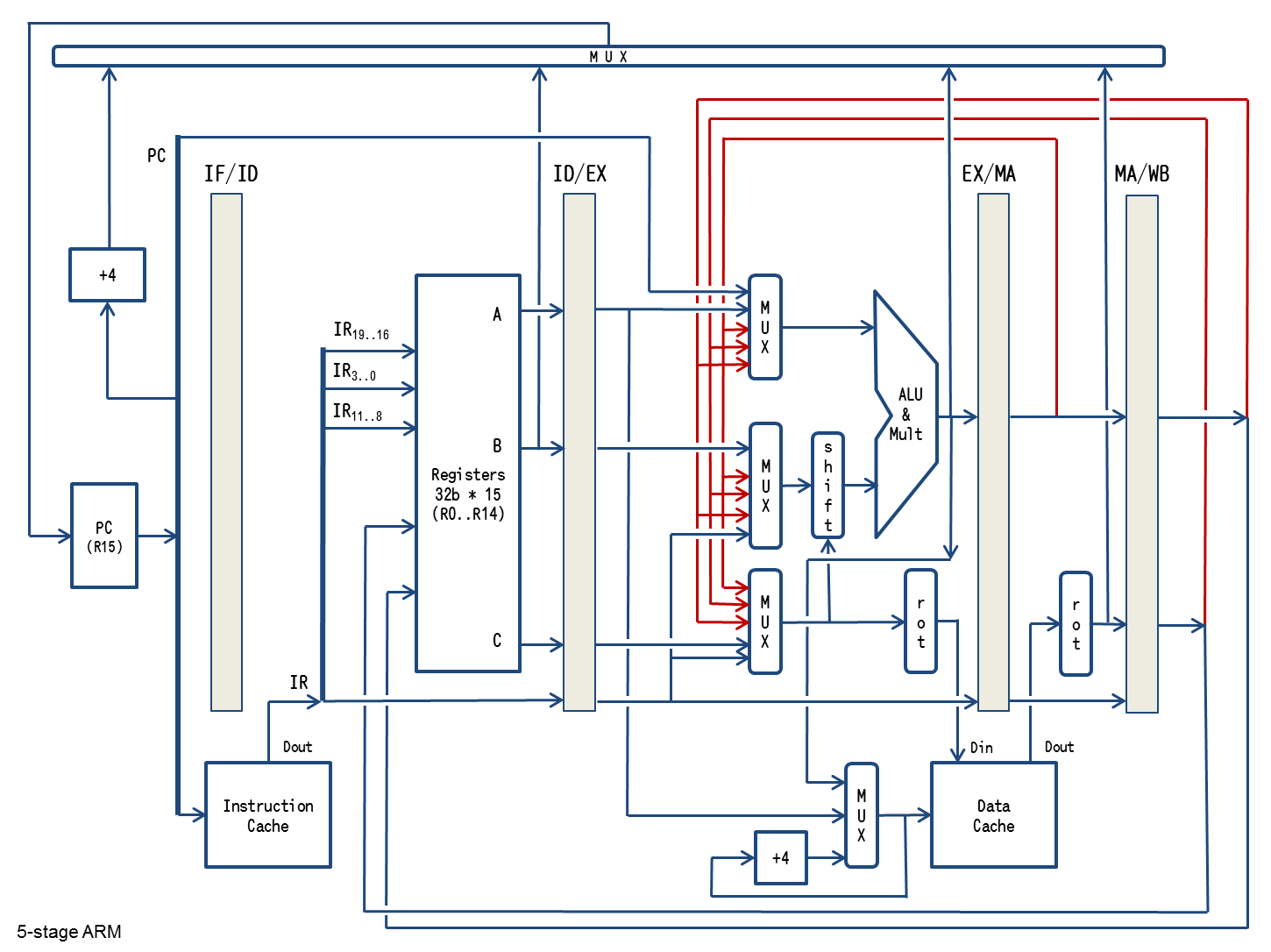

armyをベースとして、 5段パイプライン構成とすること。

基本的なパイプライン構成図は以下の図に示す。

(非パイプラインシミュレータでは、このパイプラインの各ステージを

命令サイクルの1サイクルごとに逐次的に処理している)

各ステージでの主な処理内容は以下の通りである。

(概要を示すための擬似コードであるため、必ずしも厳密なものではないことに注意)

A Simple Implementation of ARM Pipeline (w/ 5-stage)

[IF stage (Instruction fetch)]

request_read_to_cache(PC);

PC = PC + 4;

[ID stage (Instruction decode)]

IR = reply_read_from_cache(PC);

decode(IR);

A = read_source_operand_1();

B = read_source_operand_2();

C = read_source_operand_3();

[EX stage (EXecution)]

/* Memory references: */

if (U-bit is on)

ALUOutput = A + B;

else

ALUOutput = A - B;

if (IR is load-op)

request_read_to_cache(ALUOutput);

else

request_write_to_cache(ALUOutput, B);

/* Register-Register ALU Instruction: */

opr2 = calc_operand2_val(IR, B, C);

ALUOutput = A func opr2;

if (S-bit is on)

update_flags();

/* Register-Immediate ALU Instruction: */

opr2 = calc_operand2_val(IR, B, C);

ALUOutput = A func opr2;

if (S-bit is on)

update_flags();

/* Branch: */

ALUOutput = A + (B << 2);

if (L-bit is on) /* BL */

ALUOutput2 = C;

/* Branch (BX only): */

ALUOutput = A;

[MA stage (Memroy Access)]

/* Memory references (Load instruction): */

LMD = reply_read_from_cache(ALUOutput);

/* Branch: */

if (CondOK)

PC = ALUOutput;

[WB stage (Write Back)]

if (CondOK) {

/* Memory references (Load instruction): */

Regs[Rd] = LMD;

if (W-bit is on)

Regs[Rn] = ALUOutput;

/* Memory references (Store instruction): */

if (W-bit is on)

Regs[Rn] = ALUOutput;

/* Register-Register ALU Instruction: */

Regs[Rd] = ALUOutput;

/* Register-Immediate ALU Instruction: */

Regs[Rd] = ALUOutput;

/* Branch (BL only): */

Regs[14] = ALUOutput2;

}

これをベースとして、データハザードを緩和するためのデータフォーワーディング

機能や、制御ハザードを緩和するためのパイプライン制御機能を追加すること。

命令パイプラインの動作を表示する機能を付け、

実際にプログラムを動作させたときの様子を表示させよ。

(いろいろ表示を工夫してパイプラインの動作が見やすくするとよい)

キャッシュの制御を実現するために必要なデータ構造を定義し、

以下のメンバ関数を作成することで実現すればよい。

※実現の簡単化のため、

キャッシュのアドレスタグや validビット/dirtyビットなど制御部分のみを

考慮し、データ自体はメモリに対して直接読み書きするようにしているので注意。

bool has_data(sim_addr addr);int victim_way(sim_addr addr);bool victim_needs_copyback(sim_addr addr, int way);void fill_block(sim_addr addr, int way);void access_block(sim_addr addr, bool write_flag);また、以下のプログラムを使って、 ダイレクトマップ(n=1)、セットアソシアティブ(n=2または4)のときのシミュ レーションを行い、 キャッシュメモリへのアクセス回数やヒット率(あるいはミス率)を計測せよ。

行列の乗算プログラム

Cソースファイル/

逆アセンブルリスト/

ダンプテキストファイル

分岐予測の回数や成功率(あるいは失敗率)を表示する機能を付け、

実際にプログラムを動作させたときの分岐予測の性能について調査せよ。