以下の各課題プログラムを作成し、レポートせよ。

※質問・疑問は随時受け付ける。

レポート提出期限 2011年8月12日(金)

レポートは

学科授業支援システム CoursePowerで提出すること。

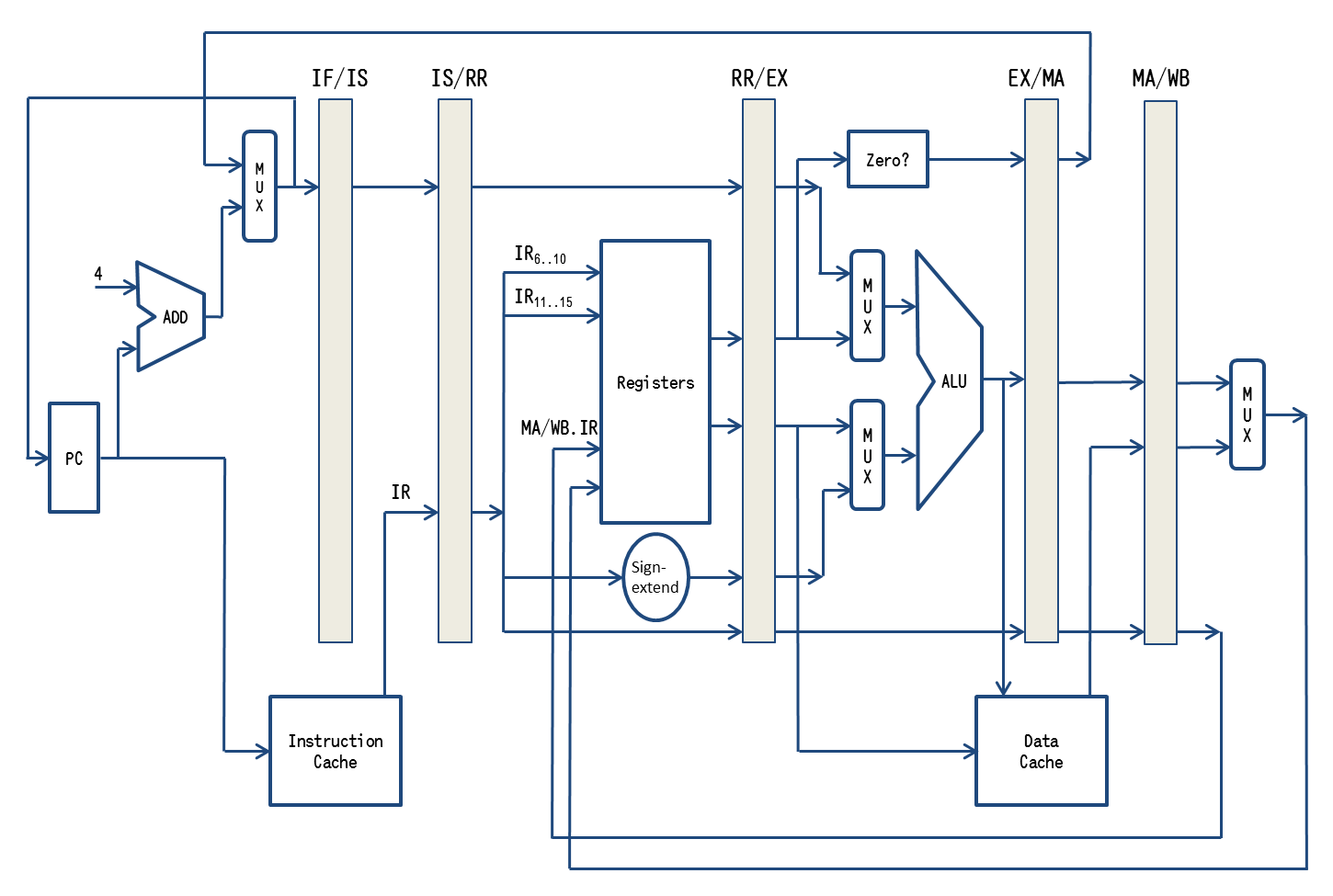

mipsyをベースとして、 6段パイプライン構成とすること。

基本的なパイプライン構成図は以下の図に示す。

(非パイプラインシミュレータでは、このパイプラインの各ステージを

命令サイクルの1サイクルごとに逐次的に処理している)

各ステージでの主な処理内容は以下の通りである。

A Simple Implementation of MIPS Pipeline (w/ 6-stage)

[IF stage (Instruction fetch First)]

request_read_to_cache(PC);

NPC = PC + 4;

[IS stage (Instruction fetch Second)]

IR = reply_read_from_cache(PC);

[RR stage (Register file Read)]

A = Regs[rs(IR)];

B = Regs[rt(IR)];

Imm = imm(IR); // sign-extended immediate field of IR

UImm = uimm(IR); // immediate field of IR

[EX stage (EXecution)]

Memory references:

ALUOutput = A + Imm;

request_read_to_cache(ALUOutput);

or

request_write_to_cache(ALUOutput, B);

Register-Register ALU Instruction:

ALUOutput = A func B;

Register-Immediate ALU Instruction:

ALUOutput = A func Imm;

Branch:

ALUOutput = NPC + (Imm << 2);

Cond = (A == 0);

[MA stage (Memroy Access)]

Memory references (Load instruction):

LMD = reply_read_from_cache(ALUOutput);

Branch:

if (Cond) PC = ALUOutput;

[WB stage (Write Back)]

Memory references (Load instruction):

Regs[rt] = LMD;

Register-Register ALU Instruction:

Regs[rd] = ALUOutput;

Register-Immediate ALU Instruction:

Regs[rt] = ALUOutput;

これをベースとして、データハザードを緩和するためのデータフォーワーディング

機能や、制御ハザードを緩和するための分岐先算出用の加算器・分岐条件判定器などを

追加すること。

紙面にて配布した資料

(Appendix-A Pipelining: Basic and Intermediate Conceptsの一部抜粋)を

参考にするとよい。

(ただし、資料では5段パイプライン構成を前提としているので、当然細部は異なる)

命令パイプラインの動作を表示する機能を付け、

実際にプログラムを動作させたときの様子を表示させよ。

(いろいろ表示を工夫してパイプラインの動作が見やすくするとよい)

分岐予測の回数や成功率(あるいは失敗率)を表示する機能を付け、

実際にプログラムを動作させたときの分岐予測の性能について調査せよ。